I am a Postdoctoral Scholar in Electrical Engineering at Stanford University, working with Prof. Subhasish Mitra in the Robust Systems Group (starting January 2026).

I completed my PhD in Electrical & Computer Engineering at the University of California, Santa Barbara (Dec 2025), where I worked on probabilistic computing with p-bits and extreme-scale distributed architectures for Ising/Boltzmann machines on CMOS/FPGA platforms.

At Stanford, my current work focuses on the Scale AI project under the Microelectronics Commons program, including 3D chip design execution and system measurement & verification for large-scale “Illusion” multi-chiplet designs.

- 3D chips

- Multi-chiplet systems

- System measurement

- Hardware verification

- Probabilistic computing

- Ising/Boltzmann machines

Research Highlights

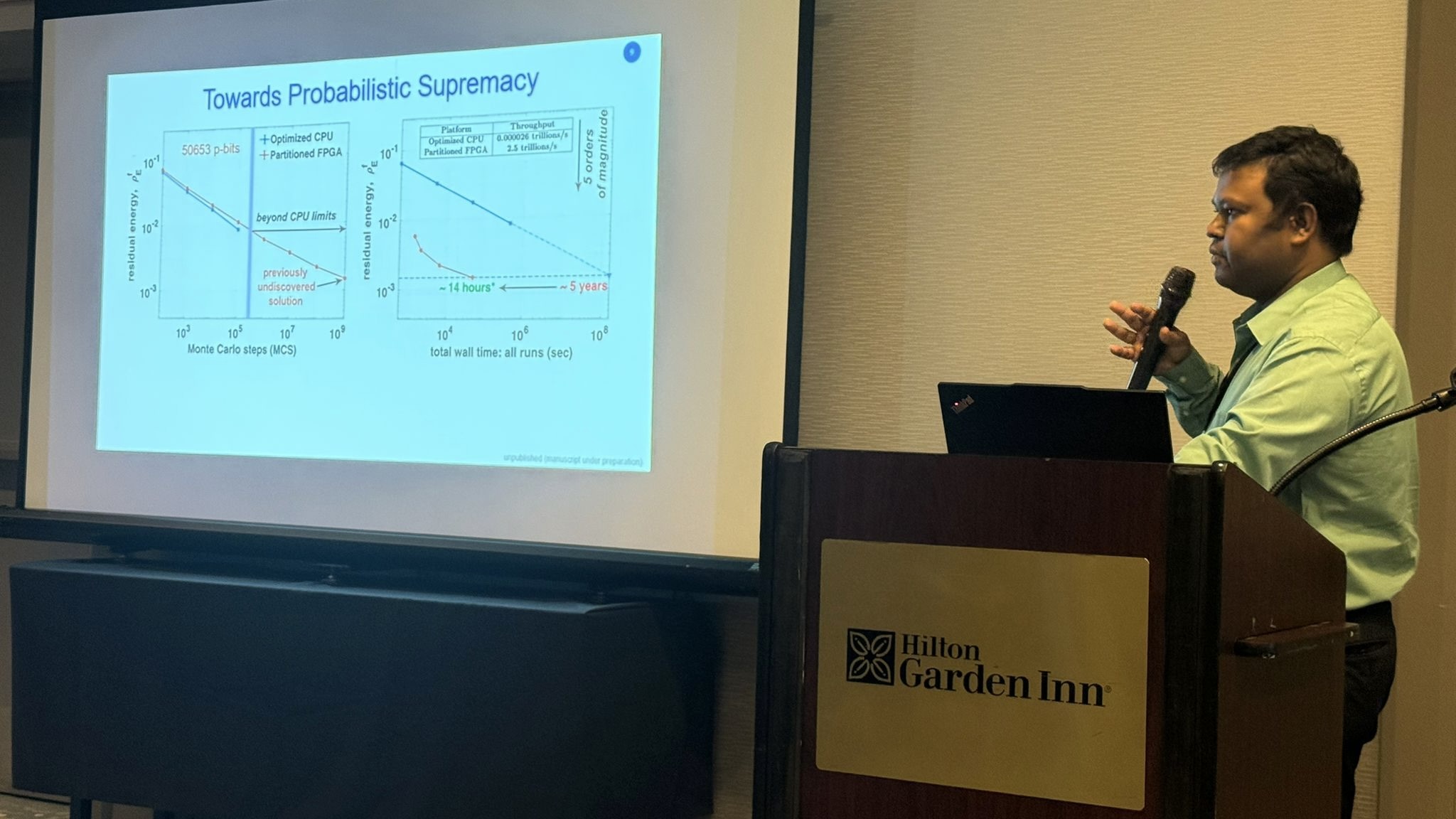

- Distributed probabilistic computing — Interconnect multi-FPGA / heterogeneous hardware over ultra-low-latency links; ~1M p-bits scaling.

- Probabilistic AI & ML — Ising/Boltzmann samplers for generative AI, Bayesian inference, and scalable energy-based ML.

- Quantum-inspired optimization — Hardware–software co-design blending probabilistic systems with quantum-classical workflows.

Key first-author papers

- Nature Electronics (2022): Massively parallel probabilistic computing with sparse Ising machines.

- Nature Communications (2024): All-to-all reconfigurability with sparse & higher-order Ising machines.

- VLSI Symposium (2023): Accelerating Adaptive Parallel Tempering with FPGA-based p-bits.

- IEDM (2022): Experimental evaluation of simulated quantum annealing with MTJ-augmented p-bits.

- IEDM (2021): Computing with invertible logic: Combinatorial optimization with probabilistic bits.

Recognition

- Misha Mahowald Prize (2025) — Official Announcement · UCSB News · YouTube · Group award with Prof. Kerem Y. Camsari (OPUS Lab).

- Bell Labs Prize (Bronze, 2023) — UCSB News · Bell Labs Blog · Team award with Prof. Kerem Y. Camsari.

- UCSB Graduate Division — PhD Dissertation Fellowship (2025) — Opus Lab News